# Hardware security for IoT identity assurance

André Cirne\*, Patrícia R. Sousa\*, João S. Resende<sup>†</sup>, Luís Antunes\*

\*Faculty of Science - University of Porto <sup>†</sup>NOVA School of Science and Technology

Abstract—The widespread use of Internet of Things (IoT) devices makes their security a priority. Among the different security challenges, identity and authentication mechanisms rise as the most important. Identity and authentication in IoT are limited by the device's computation capabilities and are more susceptible to physical attacks than common computers and servers. Regardless, identity and authentication mechanisms are essential for a secure system.

Researchers have pointed out that hardware, the source of these limitations, may also be the solution to overcome these challenges. Systems may include hardware-based cryptographic implementations to overcome computation and energy limitations. On the other hand, the addition of security hardware can increase the resilience of a device against hardware and software attacks.

Our work aims to support these claims by exploring the physical attacks and other challenges that identity and authentication are subject to and analyzing possible technologies that may solve these issues.

For achieving this goal, we preformed a threat analysis to the IoT identity and used it to guided us through the research. For each technology, we identified: known security attacks, employed countermeasures, advantages and disadvantages for identity assurance. Additionally, we surveyed the literature for examples of these technologies supporting the device's identity.

Finally, we were able to create an objective comparison between the different technologies and identified challenges that are hampering the extensive use of hardware-based identity and authentication systems in IoT.

Index Terms—IoT, device's identity, identity, hardware-based identity, hardware trust anchors, hardware attacks

# I. INTRODUCTION

The Internet of Things is an environment of interconnected devices that uses the Internet to share data. Virtually any device can be connected to the network. Smartphones, wearables, motion sensors, cars, and smart home appliances are just a few examples of connected devices today. The number of Internet of Things (IoT) devices connected to the Internet continues to grow [1] and our daily lives already depend on them. In fact, they are even replacing us in factories, farms, and other jobs [2]. This trend will not decrease and, on the contrary, continues to increase, driven by the emergence of more modern technologies emerging, such as 5G [3], Big Data [4] or Fog Computing [5], that enable better connectivity to end devices, increasing network bandwidth, storage and computing resources. Therefore, an increase in the number of Internet of Things (IoT) devices is foreseeable in the coming years [3].

With the arising of these devices, the need for strong security policies and controls in the IoT life-cycle urges [6].

IoT devices are known to be insecure and the development of security solutions is considered one of its open research challenges [7], [8]. This problem is caused by a generalized lack of security standards, along with the desire for inexpensive systems, which means security is not a priority in their development [9]–[11].

Among the different security challenges in this field [12], [13], device identity is one of the most fundamental to create a secure system. Authentication refers to the confirmation of the origin of an object or person, in this case, often related to the verification of its identity. Thus, identity management is the basis for secure authentication methods for IoT. Without these premises it is not possible to design a secure IoT system, as we lose the ability to access control resources in a system or guarantee the veracity of information received from a device [14]. Despite these facts, the issues we mentioned earlier limit the implementation of identity and authentication mechanisms, which make them custom, lacking peer review, and using slow or outdated cryptographic algorithms that do not offer the best security.

Furthermore, IoT devices are more susceptible to physical attacks than other devices, which has consequences for the creation of IoT authentication and identity systems. Unlike computers and servers, IoT devices are more likely to be deployed in unprotected locations where the attacker can have unrestricted physical access. A simple example is a smart meter placed inside the customer's home. His electric bill depends on the measurements of that device, which means that he is the person most motivated to tamper with the smart meter and has unrestricted access to it.

Approaching this problem in a general way, we can conclude that protection against physical attacks is fundamental for the production of secure IoT devices. These devices have two parts: software and hardware. The software implements all the logic of the device, while the hardware supports its execution and enables interactions with the physical world, which means that there is a relationship between them, as the software runs on top of the hardware. Regarding vulnerabilities, the industry has many tools to help us find them in software, such as code auditors, fuzzers, debuggers, and static analyzers, but there are fewer for hardware vulnerabilities. For this reason, hardware vulnerabilities are more difficult and slower to solve then their software counterparts [15].

To counterbalance, a root of trust is essentially a security process that starts with an immutable (unchangeable) hardware identity ingrained into the IoT device. A root of trust is an immutable process or identity used as the first entity in a chain of trust. For the most critical applications, a hardware root of trust can be an important building block for more secure IoT

devices. Regardless, this creates a hardware trust anchor.

This type of construction has multiple advantages, namely guaranteeing the security of the device's identity from software and physical attacks, and enabling high assurance systems, due to the higher level of resilience it offers.

As these anchors are implemented at the hardware level, there may be the wrong perception that even if the device's software is fully compromised, the attacker will not be able to compromise these primitives [16]. However, if the design can not effectively resist to hardware attacks, hackers can easily obtain the secrets of the entire chip. Attackers can use the secrets to crack identity authentication and data encryption and steal product design know-how, causing application security problems.

Therefore, there is a big demand for the implementation of hardware-level security features [15]–[18].

# A. Related Research Overview

Over the years, several literature reviews have been published on hardware security and identity that bear similarities to our work.

Yang et al. [19] reviewed different technologies that can be used to support the identification and authentication of IoT devices. Throughout their review, Yang et al. explored how each technology can be used as a building block for new systems and potential security attacks on those technologies. Our work also explores technologies with the same goal, but we include more technologies like Trusted Execution Environment (TEE)s and secure elements. Furthermore, unlike our work, Yang et al. do not compare the technologies presented.

Shepard et al. [20] reviewed technologies that allow safe and reliable execution according to the needs of IoT systems. During their analysis, they defined a threat model and evaluation criteria, focusing on the IoT use case, which was used to compare the different technologies. While our work follows a similar approach, we explore identity assurance via hardware security, which means that our analysis includes other technologies, different threats, and requirements.

Ehret et al. [21] have more generalized coverage of this topic. His research focused on hardware-based security techniques related to IoT devices. This research goes through the different components of a IoT device and presents their hardware security threats and possible mitigations. Hu et al. [22] followed the same research direction, but generalized further by presenting systems hardware security threats and their countermeasures. In addition, they reviewed security tools that can be used to verify device security, for example, to analyze at the hardware level how information flows within the board or to check if the device implementation respects its intended design. Contrarily to these works, our work analyzes the use of hardware security for a specific purpose, supporting the identification and authentication of IoT devices. In addition, we present a threat analysis specifically for this purpose and relate each threat to its identity assets. We also cover the different countermeasures for each security threat and map them onto the technologies presented.

Compared to these previous works, our research is intrinsically different from the research mentioned in this section.

To the best of our knowledge, this research is the first that connects these two realities, identity and hardware security, analyzing threats from physical security to identity, identifying potential countermeasures, and mapping them to technologies that can be used to support the implementation of new solutions.

## B. Contributions

Our work aims to provide a comprehensive analysis of hardware trust anchors that can be used to support the implementation of identity systems for IoT devices. In summary, the contributions of this research are:

- Threat analysis of physical risks to the IoT identity, which includes a definition of security assets, goals, threat actors, threats and hardware countermeasures.

- Analysis of different technologies that can be used as hardware trust anchors, containing their advantages and disadvantages, security concerns and examples of their use to support device identity.

- Discussion of challenges for adopting hardware trust anchors and future research directions.

#### C. Outline

The rest of this article is structured as follows:

The Section I-A describes similar research papers on hardware security and device identity, and how we differ from them. Section II gives a brief introduction to identity and authentication and their state of development regarding IoT. The Section III lists the different research challenges that can be retrieved from the literature related to the device identity and authentication process, and the IV section elaborates a threat analysis focused on physical risks to the device identity. In Section V, we enumerate and analyze the different technologies that can be used to support device identity. The Section VI compares the different technologies and relates them to the research challenges and security threats identified earlier. Finally, Section VIII provides a summary of our research.

#### II. TRADITIONAL VS IOT-BASED IDENTITY MANAGEMENT

One of the challenges of IoT is identity management and the effective implementation of secure authentication mechanisms. These two are fundamental characteristics to design a system with security by default, as both are security primitives to implement further features [13].

Identity is a specific set of features that allow unique identification of an entity (something or someone). There are countless implementations regarding the field of application [23]. For example, a human identity could be a fingerprint or a social security number. In the case of IoT, it can be a serial number or a cryptographic key.

Authentication is the ability of an entity to prove that it is genuinely the entity it claims to be. Thus, authentication attests to the identity of an entity. In cryptography, authentication has two main classes: data source authentication and entity authentication. Authentication of data origin refers to

information exchanges where it is necessary to ensure that the information and its source are immutable. As a result, data source authentication implies data integrity. In contrast, entity authentication is the corroboration of identity and does not include any message other than the claim to be a particular entity [24].

Depending on the literature, entity authentication is synonymous with identification or self-concept. For authors who consider identification an independent notion, identification is claiming a specific identity without presenting irrefutable evidence of this claim [24], [25]. In this work, we will treat authentication and entity identification as synonyms.

Related to identity and identification, we have Identity Management (IdM), which is the process of managing identity information and providing authentication and access control to information systems. IdM systems handle the relation between different parties, entities, Service Provider (SP), and Identity Provider (IdP). The entity is the one that claims an identity. The SP provides a service to the entity, and, finally, the IdP has three main functions, entity registration, identity storage, and authentication, which means it is responsible for the enrollment of new entities and also the authentication process whenever an entity needs to access a service [26], [27]. This fact makes the IdP the core component of an IdM.

On a IdM, an entity can have multiple identities characterized by different identifiers organized in three categories: something that only the entity and the IdP knows, such as a password; something that the entity owns, such as a serial number; and some physical characteristic of the entity, like fingerprints [26].

With the growth of IdM systems, they started to follow the isolated model - the traditional identity model in which SP and IdP functions merge, therefore, identification and authentication are done directly in the SP itself.

Isolated models are a management burden for organizations with multiple services, implying identities for each entity [27]. In the case of human identity, multiple credentials are required, decreasing user usability and weakening overall security. To respond to these problems, IdM systems began to simplify the user experience and its management, introducing the so-called centralized model.

In the centralized model, the SP is separated from the IdP. Herewith, different SPs can use the same IdP for authentication, and the entity has a single identity across multiple servers, which also eases its management.

Despite the advances made by the centralized model and its paradigms, there are still two problems. IdP servers struggle to scale, as the increase in the number of identities implies an increase in the compute and storage requirements. Also, the centralized model does not support inter-domain authentication, which is a usability problem for large enterprises [27].

The federated model solves these issues by integrating multiple IdPs in a single authentication domain - the federated authentication domain. This model is implemented by setting a group of agreements, standards, and technologies that enable a SP to recognize identities from other authentication domain's IdP or the creation of maps between identities from different IdPs [27]–[29].

Based on the federated model principles, multiple protocols support their implementation, such as SAML [30], OpenID connect [31], and full-fledged IdM systems, as Keycloak [32] and Shibboleth [33]. These are just a few examples of implementations, there are other frameworks and systems, but the ones presented here are the most widespread [34].

Security Assertion Markup Language (SAML) [30] is a XML-based protocol to exchange authentication and authorization data between a SP and a IdP, even when they are part of different authentication domains. This protocol relies on the SAML Assertion message, a XML containing all the information required by the SP about the entity and cryptographically signed by the IdP. The SP uses the IdP's public key to check the veracity of the message. Shibboleth [33] leverages the SAML protocol to implement a complete IdM solution, featuring federated Single Sign-On (SSO) capabilities.

OpenID Connect [31] is an authentication and authorization framework, which is implemented on top of the OAuth 2.0 authorization framework [35] by adding an identity layer that allows the exchange of identity information [31]. The protocol uses a REST API to delegate conditional access to entity data. The entity obtains an Access Token from the IdP that SP uses to access its identity information. Keycloak [32] is an example of a IdM system based on OpenID Connect.

The growing number of online users and accounts has driven the evolution of IdM models to be user-centric. Both protocols are examples of this paradigm. The user controls the information exchanged between SP and IdP, which allows users to have different identifiers linked to their identity, which can be shared with SPs according to their consent. Furthermore, this paradigm is being explored to create SSO experiences. The user only needs to authenticate once and will have access multiple services without having to re-enter their credentials [36].

Research continues to follow the user-centric paradigm, addressing privacy issues, such as a lack of control over personal data dissemination [37]. Others move away from the classic centralized model and make decentralized IdMs focusing on preserving user privacy [38]–[40].

With the emergence of IoT devices, the need for specific IoT IdM solutions has also increased [41]. IoT devices are inherently different from humans because there is a lack of identifiers, which makes it difficult to develop solutions.

Lam et al. [42] listed four types of characteristics that can be used to identify a IoT device: *inheritance*, *association*, *knowledge* and *context*; inheritance is the most hardware-dependent and immutable, and context is the most hardware-independent, but changeable.

The *inheritance* category is like human biometrics identifiers. It includes information dependent on the device's hardware and unique for each device. An example of an identifier of this type is a Physically Unclonable Functions (PUF) (more details in Subsection V-F).

The *association* category uses relationships between devices that are critical to their functioning. For example, if a wearable needs a connection to a smartphone to communicate with the Internet, the smartphone can be an identifier for the wearable.

The *knowledge* category is similar to the "something you know" for humans. However, the level of assurance is very different. A human can memorize a password and does not need to save it anywhere else. On the other hand, a device needs a mechanism to store the password securely, which implies risks.

Lastly, the *context* category uses IoT-based sensing data as identifiers. Context-aware computing connects much information found in the real world to the intelligence of the environment. For example, sensor readings produced by GPS sensors can be considered raw sensor data. Since we put the data from the GPS sensors in such a way that it represents a geographic location, we call it context information. However, it is necessary to consider the quality of context, which depends on the quality of the physical sensor, the context data, and the quality of the delivery process. So, these identifiers can have relatively less quality than others and introduce some challenges, such as when a device has an owner and multiple users or when the interactions with the devices change over time. Both produce changes in the identifiers that make them difficult to use [42].

Regardless of the identifiers used to authenticate a device, there is no universal identifier for IoT devices, which is a barrier to developing perfect IoT solutions. Although each resource on the Internet has a unique domain name or a public IP managed by international organizations, this does not exist in IoT, as each manufacturer has its standards and protocols. Therefore, in the short term, it is unlikely that a universal solution to this problem will emerge [43]. However, researchers are developing ways to authenticate and identify IoT devices.

Most IoT systems use cryptographic-based entity authentication, which means that device identifiers are used in conjunction with cryptographic algorithms to enable identity verification [44], [45].

An example of this type of authentication is *Attribute-Based Authentication* schemes, in which device attributes are used to generate a secret key in a public-key encryption scheme. Every time the device needs to authenticate, it encrypts a challenge sent by the server with its key. The server will then decrypt this message using the expected attributes to reproduce the device key, and if it can retrieve its challenge from the encrypted message, the device will be authenticated [42].

There are also systems using other approaches. For example, the use of private keys and Public Key Infrastructure (PKI) certificate for each device [46], or adapted versions of IdM systems to the IoT, mainly when it is necessary to authenticate devices and users [47].

Beyond that, researchers are working on blockchain-based solutions [13], [34]. These aim to create fault-tolerant IdMs, enabling unique identifiers to promote interoperability among different brands of devices [34].

As we stated earlier, most protocols rely on asymmetric cryptography and assume the availability of secure storage, which brings limitations for use in IoT. Asymmetric encryption is too heavy for low-end IoT processors, which makes encryption operations slow and energy-intensive [19], [48]. On the other hand, almost all IoT devices do not have secure

storage available due to the inherent cost or expertise required to implement these features [17]. Therefore, if we want to continue to use solutions that rely on standard cryptographic algorithms, IoT must be assisted by hardware components that ease their execution and create the necessary security conditions.

## III. HARDWARE-BASED IOT IDENTITY CHALLENGES

Since the beginning of IoT, device identity has been pointed out as an open research challenge [12], [49]. Assessing the requirements stated in the Section II, we can highlight three main research opportunities for identity management: **Lightweight Cryptography** [7], [8], [12], [49], **Object Identification** [8], [12], [41], [43], [49], and **Secure Storage** [43], [49], [50].

One of the limiting factors in IoT is its restricted resources, which limits the implementation of identity and authentication mechanisms. Several authors point out that **Lightweight Cryptography** can solve this problem [7], [8], [12] as lightweight cryptography is an encryption algorithm or protocol designed with restricted devices in mind. This type of solution is evaluated according to requirements such as energy consumption, implementation size, RAM, and computational power [51]. Lightweight cryptography does not necessarily imply a trade-off in security efficiency. Some researchers try to develop new approaches to cryptographic problems while respecting device constraints, and others use known algorithms and protocols and try to reduce them to meet the requirements of constrained devices [51].

Before designing any security system, it is necessary to be able to identify each device. An ideal identification solution should reflect the device's characteristics in its identification process [12]. For example, following the idea that IoT devices can connect to the Internet anytime and anywhere, the device identity should reflect these properties [52]. Also, regarding this issue, IoT promises that devices will communicate seamlessly regardless of manufacturer. However, the lack of standardization undermines this idea. Therefore, creating a vendor-independent identifier is a priority to overcome this problem.

Therefore, the challenge of **Object Identification** is being addressed through two different approaches. First, researchers and international organizations are trying to create a global naming scheme that multiple manufacturers can use and be able to identify a device, even when it is not connected directly to the Internet (for example, a sensor that connects to a gateway via Bluetooth ) [49], [52]. On the other hand, researchers are exploring how we can define identity by analyzing the necessary resources and available technologies.

For solving the object identification challenge, the need for **Secure Storage** resources increases. As we stated previously in this section, many identities require the storage of cryptographic keys, and independent of the method used, the identity needs to be stored securely on the device. Therefore, researchers are looking for ways to solve this problem, from creating encrypted storage to dynamically generating cryptographic keys using the intrinsic characteristics of the device [25], [50].

In summary, identity in IoT has two ways to overcome this challenge, either by using existing IdM systems and making devices capable of handling computationally demanding cryptographic algorithms or by starting to employ new IdM systems that exploit lightweight cryptography. Either way, hardware can be part of the solution.

Any of the technologies presented in this work may be used to support these research challenges. The relationship between the two is further developed in the Section VI, where we compare the different technologies and analyze their advantages and disadvantages for each research challenge.

## IV. HARDWARE-BASED IOT IDENTITY THREAT ANALYSIS

As stated earlier in this paper, IoT devices are more likely to sustain physical attacks. This trend can be hampered by developing devices resilient to this type of attack, which means that the component and design of devices must be protected from physical attacks.

A threat analysis is a process to identify the security requirements for the component of each device. This analysis is based on various characteristics, such as potential intruders, attacks, and device assets.

Developing a detailed threat profile provides organizations with a clear illustration of the threats they face and allows them to implement a proactive incident management program that focuses on the threat component of risk [53]. This threat analysis starts with defining the context of the IoT environment that will be assessed and will follow a threat profile that includes information about critical assets, actors and threats to evaluate the requirements for secure hardware-based IoT identity management.

# A. Context Environment

IoT devices have two major components: hardware and software. Physical attacks target the device's hardware. However, a hardware attack will affect the device's software due to the relationship between hardware and software.

As with any computer, IoT hardware has a CPU that provides computation capabilities, RAM to hold program storage, Read Only Memory (ROM) to store the boot program connected by a CPU bus, and multiple buses to hold peripherals, like persistent storage. However, unlike computers, IoT devices include all these components on a single chip called System On a Chip (SoC) [54], depending on the system's purpose. For example, it may have multiple WiFi and Bluetooth radios or general-purpose buses like I2C and SPI. Finally, but not least, an IoT device has its Printed Circuit Board (PCB), which provides pads to solder different components and offers a reliable electrical connection between them.

IoT devices need firmware to function. Firmware is an embedded-software in a piece of hardware. The first software to run on a device is the bootloader. The bootloader can be in the SoC, on an on-chip ROM - programmed during production - or in external memory. The bootloader is responsible for initializing the different components and transferring the execution to the user image. Depending on

the device, the user image can be an embedded Operating System (OS) or a bare-metal application [55]. If the user image is an embedded OS, the operating system will manage the different processes, events, and a hardware abstraction layer. Besides, the embedded OS is also responsible for running the applications. On the other hand, if a bare-metal application is loaded, the application will need to handle and interact with the hardware directly. The choice between an operating system or a bare-metal application will depend on the device's capabilities.

Software and hardware depend on each other, and the device will not function correctly if one of these parts is faulty. If the software stack is compromised, it does not mean the hardware was compromised. Contrariwise, hardware attacks compromise software. Moreover, an existent Over-theair (OTA) update can always patch software vulnerabilities. On the other hand, hardware vulnerabilities require a new hardware revision to solve them, so there will be devices that will never be fixed [56].

Hardware attacks require specialized knowledge and tools. Therefore, devices that do not require high assurance do not minimize these risks. Furthermore, security certifications that address these threats do not assess whether the risks are fully mitigated but assess whether the device has countermeasures to disrupt and delay the attacker [57].

Any device's components can be an entry point to compromise its identity. However, attacks on software will not directly affect the device's identity but rather the authentication protocol or will require lateral movement and further exploits to attack the device's identity.

As this work focuses on identity assurance through hardware, we will only consider identity threats related to hardware, which means hardware attacks, and attacks that can be mitigated by hardware. These threats will help us to define the security features and capabilities of the components mentioned in Section V. Moreover, during this analysis, we assume the attacker has complete access to the physical device and unlimited time to perform the attack.

# B. Assets

In a threat analysis, an asset is something that has value to the company and must be protected. For example, in the case of a pay-TV network, there is a smart card with a decryption key that will control access to the network. In this case, this smart card is an asset as it is crucial to the company revenue [58].

Our threat analysis does not have a specific product, so we will only focus on the technical assets needed to achieve identity and authentication. Any of our assets will require confidentiality and integrity, which means the assets must be kept hidden from attackers, and attackers must not be able to modify them. We are not considering its availability because we assume that the attacker has physical access to the device, which means that for this type of attacker, making a service unavailable is the same as disconnecting it from power.

As we stated at the beginning of Section II, identifiers must support the identity of a IoT device. We have listed four identifiers: context, association, knowledge, and inheritance. Context is a technique that allows identifying a device by analyzing the way the device relates to other devices and the environment that is associated with it. Regarding association, it is to something that device can possess for one or two-factor authentication, such as a hardware token. By contrast, knowledge and inheritance rely solely on the device's characteristics to create an identity. The inheritance category uses hardware characteristics to identify a device and the knowledge category encompass the information that only the device knows, such as an authentication token or cryptographic key. Therefore, these last two identifiers are prone to be compromised by hardware attacks.

For the inheritance identifier, the attacker may try to clone the **Integrated Circuit** (**IC**) design to steal its identity. Therefore, the confidentiality of the **IC** design must be protected.

On the other hand, attackers may also try to tamper with the device to bypass security features, so the **IC design** must protect its integrity.

In addition to the **IC** design, an attacker needs to have access to the device's **firmware** to clone it. Furthermore, the attacker may reverse engineer the firmware to find software vulnerabilities that can compromise the authentication mechanisms. Therefore, keeping the firmware confidential will difficult the cloning process and the vulnerabilities discovery.

Regarding firmware integrity, the main security goal is to make it impossible for unauthorized code to run on the device. This can be developed into three attack vectors. The attacker must not be able to change firmware when stored on persistent storage. If persistent storage is compromised, the device must not execute any instructions that could have been tampered with. Finally, the attacker must not be able to induce temporary changes in the execution of instructions.

Finally, knowledge identifiers, depending on the device, can be authentication tokens, passwords, cryptographic keys, or other information. During this work, we will refer to them as **identity data**.

In the case of cryptographic keys, it is essential to highlight that even if the system does not use them directly as an identifier, they can be used internally to keep information secure or authenticate data traffic. Therefore, the keys must be protected regardless of their type. For public keys, the goal is to maintain their integrity; for private keys, it is to ensure their confidentiality. Public keys are used to verify signatures and encrypt information. Therefore, if a public key is changed, it can disrupt the signature verification process, leading to various attacks, from Man-In-The-Middle (MITM) to malicious updates of OTA. The private and asymmetric keys are used to identify the device or decrypt important information. Therefore, if an attacker compromises their confidentiality, they could spoof the device's identity or MITM communications.

To conclude, devices must maintain three secure assets: CI design, firmware and identity data to protect the device's identity and authentication capabilities.

#### C. Actors

Many techniques presented throughout this section require expensive equipment, in-depth system knowledge, and execution time. Therefore, not all are within reach of all threat actors. A threat actor is someone, either a person or a group, who poses a threat [59]. Threat actors can be adapted according to their capabilities and motivation. The capabilities of threat actors are the combination of resources and knowledge available to carry out an attack. The threat actor's motivation is the level of desire to perform some action and the expectations (confidence) of success [60]. The threat actor's motivation level is related to the time it takes to succeed. A less motivated attacker will quickly give up on the target if the device has too many countermeasures that require time to circumvent. IoT devices have five main threat actors: criminal enterprises, industrial competition, nation-states, ethical hackers, and lay attackers [56]. Criminal enterprises are motivated by the financial gain they can get from an attack. Typically, these organizations look for vulnerabilities that enable solid business cases. For example, Remote Code Execution (RCE) vulnerabilities in IoT devices to increase the ability of botnets to perform Distributed Denial of Service (DDoS) attacks. Due to the nature of these organizations, the budget for these attacks is high, but their criminal status limits the human resources they can hire and the equipment they can buy.

Industrial competitors aim to collect information about a competing device, which means they reverse engineer the device. This attacker will employ skilled professionals and have an ample budget to acquire all the resources needed to carry out an attack.

Nation-states have motivations such as espionage, counterterrorism, and sabotage. This group has all the necessary means to carry out complex attacks, with the best and most significant amount of professionals, tools, and time to plan attacks.

Lay attackers are usually individuals or small groups who hack to extort money from companies or gain a reputation. Typically, these groups have limited resources and expertise, so they will look for another target if they find countermeasures.

Ethical hackers are driven by a curiosity about how a system works or by the possibility of monetary reward. Unlike lay attackers, they will not try to make money illegally but through legal initiatives, such as bug bounties. They may have the expertise to carry out complex attacks, but they have a limited budget and time. At the same time, they can gain access to more expensive equipment through universities and hackerspaces. When compared to other attackers, they pose a different kind of risk. Ethical hackers are not trying to harm a company, but if not dealt with properly, they can affect consumers' trust in a company because if a vulnerability of a known company is disclosed before it is resolved or properly explained by the company, defamation can result, and customers may no longer trust the company. The motivation and capabilities of each attacker are summarized in Table I. In this table, the attacker's capability is analyzed using two characteristics, knowledge and resources, classified as low, moderate, and extensive.

The motivation was classified as low, high, and extreme,

according to the perseverance level of each aggressor. These characteristics directly impact the attacks that each attacker can carry out.

|                      | Capal     |           |            |  |

|----------------------|-----------|-----------|------------|--|

| Threat actors        | Knowledge | Resources | Motivation |  |

| Criminal enterprise  | Moderate  | Moderate  | High       |  |

| Industry competition | Extensive | Extensive | High       |  |

| Nation-states        | Extensive | Extensive | Extreme    |  |

| Ethical hackers      | Moderate  | Moderate  | High       |  |

| Layperson attackers  | Low       | Low       | Low        |  |

TABLE I SUMMARY OF THREAT ACTORS CHARACTERIZATION

## D. Threats

Hardware attacks can be divided into two main categories, non-invasive and invasive attacks, according to the physical impact on the device. Non-invasive attacks do not require any preparation of the device to be performed, which means the attacker can access all required components without any modification of the device and does not leave any tamper evidence. By contrast, invasive attacks require the removal of the chip package and target the components inside. Such attacks require expensive tools, complex techniques, and operating at a miniature scale. Many times these attacks also imply the destruction of the chip.

In addition to these categories, some authors also proposed an intermediary class between the non-invasive and invasive attacks, called semi-invasive attacks [61], [62]. Semi-invasive attacks are a subset of invasive attacks that imply the removal of the chip package but do not require contact with its internal lines, decreasing its complexity. For the simplicity of this work, we will not distinguish these attacks from invasive attacks.

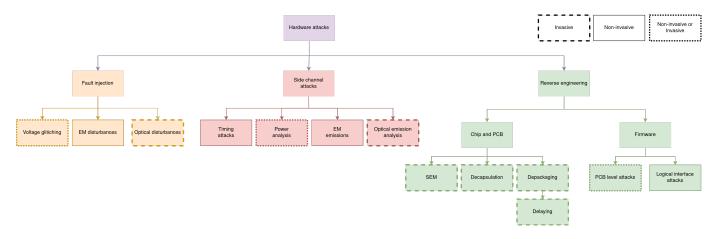

Another way to organize the attacks is in terms of similarities in the objective of the attack. This taxonomy originates three main classes of attack [62]: reverse engineering, fault injection, and side-channel attacks and eavesdropping, each containing multiple attack techniques (Figure 1).

In addition to describing possible threats, during this section, we will also present the countermeasures a device can take to difficult their exploitation. These countermeasures can either be in software or hardware. However, our main focus will be hardware countermeasures.

# Reverse engineering

Reverse engineering is analyzing a fully functional system and developing a set of specifications describing the system [63]. In IoT, there are two susceptible targets to reverse engineering, the actual hardware (components and PCB) and its firmware. With these attacks, the attacker's goal is to totally understand the device's inner workings, find vulnerabilities, or clone the device.

The attacker employs the most invasive techniques to reverse engineer the device's hardware. Decapsulation, depackaging and delayering are processes that use chemicals to

dissolve the chip package. With decapsulation, the attacker partially dissolves the package keeping the chip functional. Alternatively, depackaging completely removes the chip package and makes it non operational. Depacking enables the attacker to delayering the chip. PCBs and chips have different layers with electrical circuits, so by delayering, the attacker will polish off individual layers of the chip to better analyze them. These techniques are used to allow the reverse engineering of the device. Once a chip is exposed, an attacker can use high-resolution images or Scan Electron Microscope (SEM) to analyze it. Moreover, by applying delayering techniques, an attacker can analyze multiple chip layers [64].

Both decapsulation and SEM can be hampered by active metal shields [65] or a defensive PCB design pattern [66], [67]. An active metal shield is a metal conductive layer in the PCB that shields critical circuit elements. Depending on the shield, it can be a simple conductive layer or a meander of conductive lines with resistance sensors attached that will detect tampering, from physically probing to decapsulation attempts [65]–[68]. In terms of defensive PCB design, there are multiple techniques that can be employed. For instance, critical signals can be routed on deeper layers of the PCB and overlapped by other electrical paths that their destruction would disrupt the device's operation [66], [67].

These techniques can also be applied to reverse engineering embedded memory to extract stored information. The information stored on a masked ROM can be decoded, after decapsulation, with an optical microscope. Moreover, it is also possible to use techniques such as microprobing to monitor buses to extract information or even bypass encrypted buses by reverse engineering the chip design [69].

Micropobing is the act of attaching probes inside a chip to measure (side-channel attacks and eavesdropping) or inject voltage (voltage glitching) into an electrical line. This technique expects a decapsulated chip, which means it is an invasive technique and sometimes requires the creation of probe pads with Focused Ion Beam (FIB) [56]. FIB is a beam of ions that can either remove parts of a chip or deposit material. With this technique, an attacker can cut or reroute wires at a nanometer scale. As microprobing, FIB equipment is expensive and requires special knowledge to be performed. Despite its complexity, when successfully performed, it can circumvent many hardware security measures, such as active shields. FIB can be used to tamper with a chip or support other attacks [56], [70]. Micropobing will always depend on the success of the chip decapsulation. Moreover, a defensive PCB design that makes accessing critical signals difficult can hamper microprobing techniques.

For an attacker that is trying to reverse engineering firmware, he first needs to obtain it from the device. An attacker can leverage its access to the device's hardware and perform a PCB or logical attack.

The PCB interconnects the different components of the device. So, to extract the firmware, the attacker can connect directly to the persistent external storage with probes or desolder the memory and then use a debug tool to read it. If the attacker is able to read the firmware, he probably can write a tampered version of the firmware in the device. Another option

Fig. 1. Hardware attacks taxonomy

can be to analyze the different PCB connections and discover possible features that electrical connections can unlock. SoCs can often be booted with some security features disabled by grounding or pulling up logical pins.

Logical attacks exploit logical interfaces to communicate directly with the device's firmware, bypassing all hardware security features. Commonly, IoT devices have exposed logical ports like Joint Test Action Group (JTAG), Serial Wire Debug (SWD) or Universal asynchronous Receiver/Transmitter (UART), which allow direct interaction with the firmware or even attaching a debugger. These ports can be disabled in software, regardless, the majority of the times they are enabled. If an attacker can communicate successfully with the JTAG or SWD interface, it will be able to extract the firmware and interact with its execution. If it is UART, depending on the exposed software and device's settings, it may require further exploitation to obtain the device's firmware.

After having access to the device firmware, the reverse engineering process is similar to software. The process is the same, but researchers need to know the device architecture and how the firmware interacts with the hardware, which is often overlooked in other forms of reverse engineering due to the abstraction provided by operating systems.

# Fault injection

Fault injection is an attack that induces processing errors in a processor, forcing the processor to jump the execution of an instruction or change the content of a register.

There are multiple ways to create these faults. The more common ones are voltage glitching and electromagnetic and optical disturbances (also called laser glitching). These attacks are non-invasive, with the exception of optical disturbances, which are invasive attacks. They all have the same objective; however, the attack vector changes.

Voltage glitching is when an attacker causes a fast change in a device's component to affect its operation. Usually, this attack is executed against a power supply or a clock signal. This attack does not imply any invasive process. It is carried outside the component's package without any physical modification. This kind of attack aims to push the hardware to induce an error in the software. A simple example of this type of attack is documented by Colin O'Flyn [71], which with a paper clip, performed a power glitch to a Philips Hue Bridge 2.0's Electrically Erasable Programmable Read-Only Memory (EEPROM) to interrupt the communication between the memory module and processor. With this fault, he was able to interact with the bootloader shell that is locked. However, the majority of these attacks are more complex. For instance, force the processor to jump the execution of an instruction.

Usually, voltage glitching is a non-invasive technique. However, it can also be performed at a nanometer scale by attacking voltage lines inside a chip (microprobing). As we stated before, this technique makes the attack invasive since it requires decapsulation of the chip.

Electromagnetic disturbances are when an attacker generates electromagnetic (EM) signals and directs them to cause faults. This is possible because changes in a magnetic field near a chip induce alterations in the voltage, which can temporarily cause flips in the logical levels of a data line.

Optical disturbances leverage the fact that when a transistor is illuminated with a photon intense light pulse, it conducts current, which can be used to generate localized faults. This attack requires decapsulation of the component and lasers to emit light pulses.

Fault injection attacks jeopardize the code integrity of the device by executing the code in an unintended way. These attacks are momentary and not persistent by nature but can be leveraged to produce persistent errors, for instance, by attacking the storage interface [72]. Overall, fault injection attacks require knowledgeable and highly motivated attackers since these attacks need to be tuned by experimentation according to the target hardware, which is time-consuming. Moreover, electromagnetic and optical disturbances involve high voltages and lasers, which can hurt the attacker if the necessary safety measures are not taken.

Generally, devices can prevent this type of attack by applying software or hardware countermeasures. In terms of software, there are multiple recommendations that developers may follow. For instance, random delays can be added to the code to deflect exploitation, or critical information may be checked multiple times during execution (for instance, two copies of the same information stored in different memory regions) to detect

any exploitation attempt [73]. The duplication principle may also be applied to hardware. For example, the device can have the same function implemented in multiple places and compare their output to detect tampering attempts. Nevertheless, this type of approach is expensive [68].

Besides these general countermeasures, there are also specific techniques for each threat. Devices may have voltage sensors or monitor the clock signal to detect voltage glitching attacks [74], [75]. Power or clock lines are scattered throughout the PCB. Therefore, any attack attempt will propagate over these lines, making the attack easily detectable. On the other hand electromagnetic attacks are localized, which makes them difficult to detect [76]. EM sensors may be used to detect electromagnetic fault injections [75], [77]. However, their placement must be properly analyzed due to their limited range. On the other hand, electromagnetic fault injections can be avoided by using an active metal shield that protects the SoC from electromagnetic waves and optical disturbances [68], [78].

#### Side-channel attacks

Side-channel attacks are non-invasive attacks that aim to extract secrets from a system by measuring and analyzing physical parameters like time, power or electromagnetic emissions [79]. The majority of these attacks require the plaintext and correspondent ciphertext to be known by the attackers.

Timing attacks exploit data-dependent execution time differences to uncover secret data [79]. For example, in a password check, if a system compares the password inserted by an attacker with the correct password character by character, an attacker could measure the time it takes from the password being inserted to the feedback received. With these measurements, an attacker could reduce the effort of a brute-force attack by brute-forcing each password character thanks to the different execution times depending on each number of correct characters in his input. Depending on the target, this attack could be performed by timing responses on its software interface [80] or measuring CPU cycles [81]. The developer must mitigate this threat at the software level by ensuring the same response time independently of the input correctness.

The power consumption of a processor depends on its current activity, mainly when there are changes in the state of its components. A precise measurement of the power consumption allows an attacker to identify the current instruction and estimate changes of bits in memory [61]. Many power analysis techniques can be used to attack cryptographic systems. However, the two primary techniques are Simple Power Analysis (SPA) and Differential Power Analysis (DPA) [61].

SPA relies on the direct observation of power consumption and requires the attacker's specific knowledge about the cryptographic algorithm implementation to succeed. DPA is a technique that does not require this previous knowledge. It leverages statistical analysis to extract information from a data set of power traces [82]. Despite not requiring too expensive equipment, power analysis requires a skilled attacker.

An example of an attack using this technique was when a group of researchers extracted the cryptographic keys used to encrypt and verify firmware updates of a smart bulb through power analysis, which enabled attackers to upload a malicious OTA update [83].

To prevent these attacks, boards may use voltage regulators to keep their power consumption steady independently of the operations that are running. Nevertheless, attackers may bypass this by probing inside the chip (microprobing) [75]. This process would require decapsulation.

Integrated circuits in operation emit electromagnetic waves. The principle behind electromagnetic analysis is very similar to power analysis. It is possible to identify events by analyzing the electromagnetic signals around a device with electromagnetic probes. Furthermore, in the case of electromagnetic analysis, we can also identify the location of a specific activity by locating the source of that radiation, which is not possible in power analysis. Finally, similar to power analysis, there are multiple techniques to analyze these measures. The main ones are Simple Electromagnetic Analysis and Differential Electromagnetic Analysis, which are similar to their power analysis counterparts [79].

Optical emission analysis studies emitted photons by transistors that change state. Once again, there are two main techniques, simple and differential analysis [84], which can be used to retrieve cryptographic keys. Additionally, optical emission analysis allows attackers to locate the emission source of this photon, which means it can support reverse engineering efforts. Finally, these attacks require direct observation of the different components of the chip. Therefore the chip needs to be decapsulated. Moreover, these attacks require custom build tools to be performed, increasing the knowledge required to execute this kind of attack [56], [85].

A possible mitigation for electromagnetic and optical emission analysis is to use an active metal shield to protect critical components. In the previous subsection, we explained that these shields hinder EM and optical injections. Additionally, this type of shield prevents emissions generated inside the package from propagating to the outside, thus, preventing leakages [68], [86].

Similar to injections, some software measures, such as random delays during execution, can be implemented to decrease the risk of successful side-channel attacks [73].

Side-channel attacks mainly affect the confidentiality of identity data. The actors that perform these attacks have extensive knowledge of statistical analysis and the target's cryptographic implementations. Regarding resources, both time, power, and electromagnetic emission analysis require the same equipment, an oscilloscope, and the necessary probes. By contrast, optical emission analysis requires specialized equipment and decapsulation of the chip.

#### **Eavesdropping**

Depending on the device's design, an attacker could eavesdrop on information from the buses connecting the different device's components. This technique could be invasive or non-invasive, depending on the attack scale and if the buses are exposed or not. In a non-invasive form, this attack only requires a logic analyzer, which is not expensive depending on the number of probes. If an invasive approach is required, an attacker must use microprobing [87]. Either way, the attacker

needs to be able to reverse engineering the signals and convert them to meaningful information.

The simpler forms of this attack can be prevented by a defensive PCB design, which means critical signals should not be routed on the top or bottom layer of the PCB. This way, the attacker is forced to be invasive and perform more complex techniques such as decapsulation and microprobing to reach the same goal, eavesdropping on a signal. Nevertheless, if the signal is critical to the device, the designer should evaluate its encryption [67].

## E. Summary

Multiple attacks based on hardware can compromise the device's identity and authentication capabilities. Throughout this section, we analyzed the different security objectives to keep the IoT identity and authentication secure. At the same time, we listed the attacks that may be used to compromise these devices and detailed their requirements regarding knowledge and resources. These facts have a direct repercussion in which attack a specific threat actor may employ.

Table II summarizes the different attacks by mapping the requirements needed by the attacker to be successfully. Also, it identifies the compromised assets and outlines the hardware countermeasures. In this table, we included microprobing and FIB as they can be applied to multiple attacks and will impact its requirements.

During Section V, we will use the countermeasures identified in this section to assess the level of security of each technology against hardware attacks.

## V. HARDWARE TRUST ANCHORS TECHNOLOGIES

We have identified six technologies that can be used as building blocks to overcome today's open research challenges IoT, True Random Number Generator (TRNG)s, ROMs, crypto accelerators, secure elements, TEEs, and PUFs. For each technology, we look at its advantages and disadvantages for supporting device identity, the existing security attacks and countermeasures that are typically implemented, and finally, the systems where they have already been used to support device identity.

Before analyzing each one, we must reflect on their nature and how they relate. We can differentiate two distinct groups in these technologies: basic and composite building blocks.

Base blocks provide elementary resources, and composite blocks provide multiple resources, which means they can be broken down into smaller building blocks. For example, a TRNG is a base block as it only provides random numbers. On the other hand, a secure element is a composite building block because it provides various features such as cryptographic operations and random number generation, which are provided by base blocks, namely a cryptographic coprocessor and TRNG.

# A. True Random Number Generator

Encryption is the foundation of identity and authentication solutions. These systems rely on unpredictable and unreproducible key streams to generate cryptographic keys and produce authentication challenges, among other things. There are two random number generators types: True Random Number Generator (TRNG) and Pseudorandom Number Gnerator (PRNG). However, for cryptographic operations, PRNGs are not recommended because of their lack of entropy [88].

TRNG is a random number generator that can generate random numbers, without any periodicity, from physical sources. The TRNGs are distinguished from the PRNGs, used in most systems, by the quality of the generated numbers. A PRNG uses algorithms to generate a sequence of numbers that depends on the initial seed given to the algorithm. The numerical sequence of a PRNG is deterministic, which means that an attacker can calculate the PRNG sequence if the seed is known. Therefore, the seed must be random.

On IoT devices, seed generation have limited entropy sources, and attackers can have physical access to the device, allowing them to disrupt these sources. Therefore, TRNG can be used to overcome these problems by extracting entropy from the device environment, such as electronic noise [19]. Examples of these electronic noises are the variations of signals generated by electronic oscillators, which can be sampled, filtered for possible interference and quantified as digital bits [89]. However, this construction requires several oscillators to produce a high quality number [88], which increases production cost and energy consumption [19].

Electronic noise can suffer external interference, affecting the quality of the generated numbers. Therefore, researchers have been using quantum theory to support new TRNG constructs to solve these problems. In quantum mechanics, each choice is random and independent of the other. Based on this, researchers have been using light pulses and analyzing each photon's choice or using the time between an element's radioactive decay to create TRNGs [90].

# 1) Security attacks and countermeasures:

TRNGs, as a component, is normally embedded in a device. Therefore, it does not include security countermeasures and delegates them to the device. Depending on the type of TRNG, some attacks leverage the environment bias of these components to generate weak numbers. For instance, Ring Oscilator (RO)s based TRNGs can be biased with EM fault injections [90], at the same time, attackers can perform EM side-channel analysis to retrieve information about its internal state [91].

# 2) Advantages and disadvantages for identity assurance:

IoT suffers from a lack of available entropy. Therefore TRNGs can be the solution to provide high entropy numbers in an IoT platform.

On the other hand, TRNGs have several disadvantages. They increase the cost of the device and its power consumption. Moreover, common TRNGs that do not use quantum physics are susceptible to environmental biases, which means threat actors with physical access to the device can take advantage of this fact and attack the generated numbers.

#### *3) Implementations:*

TRNGs are included as a base component of other more complex. For instance, any identity system that uses a Trusted Platform Module (TPM) or Secure Element (SE) will inher-

|                           |                 |           | Identity as     | ssets     |                 |           | Rec        | uired capabili | ties       |                                                                       |          |          |          |          |          |     |      |                   |

|---------------------------|-----------------|-----------|-----------------|-----------|-----------------|-----------|------------|----------------|------------|-----------------------------------------------------------------------|----------|----------|----------|----------|----------|-----|------|-------------------|

| Threats                   | Identity of     | lata      | Firmwa          | re        | IC design       | gn        | Knowledge  | Resources      | Motivation | Hardware Countermeasure                                               |          |          |          |          |          |     |      |                   |

|                           | Confidentiality | Integrity | Confidentiality | Integrity | Confidentiality | Integrity | Kilowieuge | Resources      | Motivation | ı                                                                     |          |          |          |          |          |     |      |                   |

| Voltage glitching         | No              | No        | No              | Yes       | No              | No        | Madanas    | Madanata       | Madagata   | Moderate                                                              | Madagata | Moderate | Moderate | Moderate | Moderate | Low | High | - Voltage sensors |

| voltage gittening         | INO             | No        | NO              | ies       | NO              | l No      | Moderate   | Low            | riigii     | <ul> <li>Clock signal sensors</li> </ul>                              |          |          |          |          |          |     |      |                   |

|                           |                 |           |                 |           |                 |           |            |                |            | - Multiple voltage sensors                                            |          |          |          |          |          |     |      |                   |

| EM disturbances           | No              | No        | No              | Yes       | No              | No        | Moderate   | Moderate       | High       | - Active metal shield                                                 |          |          |          |          |          |     |      |                   |

|                           |                 |           |                 |           |                 |           |            |                |            | - EM sensor                                                           |          |          |          |          |          |     |      |                   |

| Optical disturbances      | No              | No        | No              | Yes       | No              | No        | Extensive  | Extensive      | High       | - Active metal shield                                                 |          |          |          |          |          |     |      |                   |

| Timing attacks            | No              | Yes       | No              | Yes       | No              | No        | Moderate   | Low            | High       |                                                                       |          |          |          |          |          |     |      |                   |

| Power analysis            | Yes             | No        | No              | No        | No              | No        | Moderate   | Low            | High       | <ul> <li>Voltage monitoring</li> </ul>                                |          |          |          |          |          |     |      |                   |

| EM emissions analysis     | Yes             | No        | No              | No        | No              | No        | Moderate   | Low            | High       | - Active metal shield                                                 |          |          |          |          |          |     |      |                   |

| Optical emission analysis | Yes             | No        | No              | No        | No              | No        | Extensive  | Extensive      | High       | - Active metal shield                                                 |          |          |          |          |          |     |      |                   |

| SEM                       | No              | No        | No              | No        | Yes             | No        | Extensive  | Extensive      | High       | <ul> <li>Active metal shield</li> <li>Defensive PCB design</li> </ul> |          |          |          |          |          |     |      |                   |

| Decapsulation             | No              | No        | No              | No        | Yes             | Yes       | Extensive  | Extensive      | High       | - Active metal shield<br>- Defensive PCB design                       |          |          |          |          |          |     |      |                   |

| Depackaging               | No              | No        | No              | No        | Yes             | Yes       | Extensive  | Extensive      | High       | <ul> <li>Defensive PCB design</li> </ul>                              |          |          |          |          |          |     |      |                   |

| Delaying                  | No              | No        | No              | No        | Yes             | Yes       | Extensive  | Extensive      | High       | <ul> <li>Defensive PCB design</li> </ul>                              |          |          |          |          |          |     |      |                   |

| PCB level attacks         | Yes             | Yes       | Yes             | Yes       | No              | No        | Low        | Low            | Low        |                                                                       |          |          |          |          |          |     |      |                   |

| Logical interface attacks | Yes             | Yes       | Yes             | Yes       | No              | No        | Low        | Low            | Low        |                                                                       |          |          |          |          |          |     |      |                   |

| Eavesdropping             | Yes             | Yes       | Yes             | Yes       | No              | No        | Moderate   | Low            | Low        | - Defensive PCB design                                                |          |          |          |          |          |     |      |                   |

| Microprobing              | N.A.            | N.A.      | N.A.            | N.A.      | N.A.            | N.A.      | Extensive  | Extensive      | High       | - Defensive PCB design                                                |          |          |          |          |          |     |      |                   |

| FIB                       | N.A.            | N.A.      | N.A.            | N.A.      | N.A.            | N.A.      | Extensive  | Extensive      | High       |                                                                       |          |          |          |          |          |     |      |                   |

TABLE II

RELATION BETWEEN THREATS, ASSETS AND REQUIRED CAPABILITIES

ently use a TRNG since TRNGs are fundamental part of these components.

An example of the explicitly use of TRNGs in identity systems is the work of Yang Su et al., in which a decentralized machine identifier for electric vehicles was developed employing a TRNG module for the generation of the vehicle identification [92].

# B. Masked ROM and OTP memories

Non-Volatile Memory (NVM) is a type of memory used in devices to store information persistently. There are multiple families of NVM which differentiate themselves by the employed technology and the number of times they can be rewritten. Among the different types, the ones that only allow a single write operation may be used in a system to support security operations. For instance, it can be used to implement a Root-Of-Trust (RoT) or store public keys [93].

There are four types of one-time writable memories, masked ROMs, floating-gate One-Time-Programmable (OTP)s, fuses OTPs, and anti-fuses OTPs. These last three are called OTP memories because they can be programmed in the field, offering more flexibility than a masked ROM, which can only be set during fabrication [94].

Masked ROMs have the information hardwired in the chip design, which means the data to store needs to be known before the production of the component since its electrical connections are rearranged to represent the information that needs to be stored. The significant advantage of this type of memory is its low production cost when a large amount of memories storing the same information is required. At the same time this is a disadvantage for small deployments [93], [95].

Floating-gate memory is a type of memory that leverages floating-gate transistors to store information, allowing them to be reprogrammed and erasable in the field [96].

Floating-gate memories can be erased by exposing them to a source of Ultraviolet (UV) radiation. This is possible since the packages of these memories have a quartz window that can be uncovered to irradiate the floating-gates [93]. Floating-gate OTPs follow the same working principle of floating-gate memories but have the floating-gates shielded to ensure they are not reset by radiation.

Eletric-Fuse (eFuse) OTP memory is constructed with a set of fuses that are blown to represent data. This operation is done by applying a high voltage to the fuse, which can be done in the field [97]. The working principle behind an eFuse is electromigration, the process by which material is gradually transported in a conductor. eFuses are constituted by conductive metal lines that, when exposed to high voltages, resistance increases and makes the circuit open due to electromigration [98]. However, in terms of data retention, electromigration introduces disadvantages. eFuses are susceptible to re-growth issues, where metal lines unintentionally connect, changing the stored data [99].

Anti-fuse OTP memory is similar to the Fuse OTP but uses an anti-fuse on its construction. An anti-fuse is an electronic component that, when unaltered, does not conduct electrical current, but after being exposed to a high voltage, it becomes conductive. This change is used to store information permanently in memory [97].

# 1) Security attacks and countermeasures:

The main objective of read-only memories is to make data unchangeable. With the exception of floating gate OTPs, there are no known attacks to this part. As we stated before, since floating gate OTPs are based on floating-gate memories, attackers may try to bypass its shield and expose it to UV radiation to be able to write it again [100]. eFuses suffer from the re-growth issues, but we have not found any literature exploiting this fact to create an attack to compromise the OTP.

On the other hand, since these memories have information that can be interesting to an attacker, it is essential to assess how easy it is to retrieve the stored information. The presented memories have very similar protection levels. To retrieve the information, an attacker must depackage and delaying the chip and then use an high-resolution optical microscope to read its information manually [69], [100]–[102]. Another option is

to use an SEM to retrieve the information. However, this is not possible on anti-fuse OTPs [98]. All these techniques are invasive, requiring expensive equipment and manual work to retrieve the memory data.

To mitigate these risks, device designers employ active shields protecting the memories that will erase their content or damage the device if any tampering attempt is detected. Nevertheless, if not backed up by batteries, this kind of protection will only work if the device is power-on. Therefore it will not stop offline attacks.

## 2) Advantages and disadvantages for identity assurance:

Masked ROM and OTP memories are cheap options to store information that can only be read. Despite that, they also have several security risks which cannot be ignored for high assurance deployments. An attacker with physical access to the device can replace these with similar ones but with different content since devices do not have mechanisms to ensure the integrity of the memory itself. Moreover, for each memory type, specific attacks can be leveraged to change the content of these memories [101], [103]. Therefore, masked ROM and OTP memories bring advantages for systems that require a low-security assurance level. However, if these components are used for other assurance levels, their security risks need to be mitigated.

# 3) Implementations:

Masked ROM and OTP memories are used as building pieces for more complex systems. The most common use of these memories is to provide a RoT, which is why they are included in most SEs (Subsection V-D) [104]. More recently, researchers have been using these components as RoT in the Arm Trust Zone system (Subsection V-E) as they do not provide a default secure way to store information [105]. Another use for these memories is to enable and disable features in a device. For instance, many SoCs use fuses to disable debug capabilities, such as a JTAG or UART port [17].

# C. Crypto accelerators

Crypto accelerators offer a high throughput in cryptographic operations. These components may or may not include countermeasures against known attacks and are mentioned in the literature with multiple names, such as a custom processor and crypto array [106]. We will follow the Bossuet et al. [106] taxonomy and present four types of components: General Purpose Processor (GPP)s with crypto acceleration, hardware crypto coprocessors, crypto processors, and crypto arrays.

GPPs with crypto acceleration are Central Processing Unit (CPU)s that have dedicated instructions for cryptographic operations. These specialized instruction sets allow programs to take advantage of dedicated hardware for cryptographic operations, which is faster than running these operations on a general-purpose hardware. However, this type of solution does not offer any other feature, which means it depends on the GPP for secure storage and preventing hardware attacks.

The crypto acceleration in these GPPs is usually implemented using specialized Arithmetic Logic Units inside the GPP to provide a low overhead connection to the GPP using internal buses.

Examples of GPPs with crypto acceleration are the Intel CPUs with the AES-NI instruction set [107] and ARM CPUs with the ARMv8 Cryptography Extension [108].

Hardware crypto coprocessors are a logic devices or hardware modules dedicated to executing cryptographic operations. These coprocessors cannot be programmed are entirely dependent on a processor to operate, to the point of not having any storage to store secrets. However, these components are more flexible than GPPs with crypto acceleration, enabling reconfiguration of the algorithms, since they are typically implemented on top of Field-Programmable Gate Array (FPGA)s [106].

A crypto processor is an independent processor that is specialized in cryptographic operations. In contrast to GPPs, these processors protect their secret keys. The keys are typically generated inside the processor, stored in a dedicated memory, and transported in a dedicated bus. All these measures are implemented to ensure that the system can only interact with the key by performing a cipher or decipher operation [106], [109]. Nevertheless, countermeasures against more intrusive attacks will vary according to the mode.

An example of a crypto processor that can be found in the majority of the computers is the TPM.

Hardware TPMs are secure crypto processors that implement a specification that the Trusted Computing Group (TCG) created to establish trust in a computation system. Namely, hardware TPMs must have the appropriate hardware protections to provide three RoTs, storage, measurement, and reporting [110], [111].

TPMs have registers to store measurements of each software that runs during the boot process of a system. These measurements provide a chain of trust, allowing detection of any tampering attempt of the boot process. In addition to that, they have a set of asymmetric key pairs which can be used for encryption and signing [110]

These two features allow the production of signed reports of the system's software configuration and, at the same time, decipher data only when the system matches a specific state, which is the base for Trusted Computing.

TPMs offer a secure random number generator and cryptographic engines according to their version. For instance, the most recent version, 2.0, offers RSA, ECC and AES cryptography engines. All these features are backed up by tampering-resistant hardware. [112]